1、???

輸入信號

??

clk :

時鐘(每個象素點的顯示時鐘)

?? reset :

復位信號

2、???

輸出信號

???

vga_hs_control?????????????????? :?????

行同步

?

??????? vga_vs_control?????????????????? :?????

場同步

;

??????? vga_read_dispaly ????????????? :?????

紅

??????? vga_green_dispaly????????????? :?????

綠

??????? vga_blue_dispaly?????? :??

藍

3、???

技術參數

clk : 24M?? hs : 30KHZ?? vs : 57.14HZ

??

設計原理

VGA(

視頻圖形陣列

)

作為一種標準的顯示接口得到廣泛的應用

,

一般有專用芯片,本實驗采用

FPGA(

現場可編程門陣列

)

設計

VGA

接口可以將要顯示的數據直接送到顯示器,節省了計算機的處理過程,加快了數據的處理速度,節約了硬件成本。

顯示適配器有多種形式,它可按照所符合的視頻顯示標準來分類,業界制定了多種顯示標準,從最初的

MDA

經歷了

CGA

,

EGA

,

VGA

,

XGA,SVGA

等的發展過程。與相應的顯示適配器標準相配的顯示器也稱之為

EGA

,

VGA

,

XGA

顯示器等。實際上顯示器的標準主要反映在它們的接口,顯示功能和行,場工作頻率上。

CRT

顯示器的掃描方式

(1)???

當柵掃描方式

從上向下依次順序掃描

完一場稱逐行掃描。一行用行頻控制(

hs

)

,

一場用場頻控制(

vs

)。掃完一行回來叫行消

隱,掃完一場回來叫場消隱

(2)???

隨機掃描方式

?

VGA

接口標準

時鐘頻率:

25

.

175 MHz(

像素輸出的頻率

)

;行頻:

31. 469 Hz

;場頻:

59

.

94 Hz

。?

?

設計

VGA

設計

VGA

圖像顯示控制需要注意兩個問題

L2]

:一個是時序的驅動,這是完成設計的關鍵,時序稍有偏差,顯示必然不正常,甚至會損壞彩色顯示器;另一個是

VGA

信號的電平驅動。顯示控制器設計提示:顯示器技術規格提供的行頻一般在

30 kHz 45 kHz(

保守數據

)

,場頻一般在

50 Hz

~

75 Hz(

保守數據

)

。針對以上保守數據,設計分辨率為

640x480

的顯示接口(如圖

4

所示),以

30 kHz

的行頻進行掃描時所需時鐘頻率為:

30 kHz

×

800(

行周期

)=24 MHz

,則場頻為:

30 kHz

÷

525(

場周期

)=5.14 Hz

。本實驗實現在顯示器上顯示彩條的設計,初始時時

GRB=

“

000

”,用一記數器過一段時間使

R

取反,即變為紅色。這樣就有黑、紅彩條了。

?

?

|

?

|

黑

?

藍

?

紅

??

品

?

?

?

綠

??

青

?

黃

?

白

?

???????????????

|

|

R

G

B

|

?0?? 0?? 0???? 0??? 1??? 1?? 1?? 1

?0?? 0?? 1???? 1??? 0??? 0?? 1?? 1

?0?? 1?? 0??? ?1??? 0??? 1?? 0?? 1??????????????

|

?

??

實驗驗證

1、

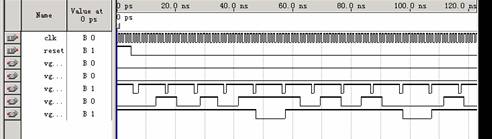

仿真時序圖

?

?

2、

驗證平臺及芯片

Xilinx

公司的

Xilinx Project Navigate

下載芯片為:

Xilinx Sparan2/xsc200

?

小結

1、?

技術難點

顯示器顯示原理、

VGA

接口原理的理解

?????? 2

、設計技巧

3

、不足或改進措施

不足:功能單一(彩條顯示)

改進:添加字符顯示、圖象顯示、圖形顯示模塊

??

參考資料

1 蔣本珊. 計算機組成原理與系統結構 北京航空航天大學出版社 p192-p198

2 陳姚節 盧建華. 基于FPGA的VGA顯示接口的研究與設計

??

源程序

library ieee;

use ieee.std_logic_1164.all;

USE ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity vga is

?????? port(

????????????? reset?????????????????????????????????? :????? in???? std_logic;

????????????? clk ???????????????????????????? :????? in? std_logic;

????????????? vga_hs_control??????????????????? :????? out std_logic;

????????????? vga_vs_control??????????????????? :????? out std_logic;

????????????? vga_read_dispaly ???????? :????? out std_logic;

????????????? vga_green_dispaly???????? :????? out std_logic;

????????????? vga_blue_dispaly?????????? :????? out std_logic?????????

?????? );

end vga;?

ARCHITECTURE a OF vga IS

?????? SIGNAL hs: STD_LOGIC;

?????? SIGNAL vs: STD_LOGIC:='1';

??? SIGNAL GRB: STD_LOGIC_VECTOR(2 DOWNTO 0);

BEGIN

PROCESS (clk) --clk = 24MHZ? hs = 30 Khz vs = 57hz

?????? VARIABLE i??? :????? integer range 0 to 799:=0;

?????? VARIABLE j??? :????? integer range 0 to 79:=0;

BEGIN

?if reset = '1' then

?? GRB <= "000"; i:=96; j:=0;? hs <= '1';

?????? elsif clk'event and clk = '1' ?then

??????

? if i < 96 then

??????

???? hs <= '0';

??????

? elsif i = 799 then

??????

???? i:=0;

??????

? else

??????

???? hs <= '1';

??????

? end if;

??????

? if j = 79 then

??????

???? GRB(1) <= not GRB(1);

??????

???? j:=0;

??????

? end if;

??????

? i:=i+1;

??????

? j:=j+1;???????? ? ???

?????? end if;

?????? vga_hs_control <= hs;?

END PROCESS ;

PROCESS (hs)

VARIABLE k?? :????? integer range 0 to 524:=0;

BEGIN

if reset = '1' then

?? k:=2; vs <= '1';

?????? elsif hs'event and hs = '1' then

??????

??? if k < 2 then

??????

?????? vs <= '0';

??????

??? elsif k = 524 then

??????

?????? k:=0;

??????

??? else

??????

?????? vs <= '1';

??????

??? end if;

??????

??? k:=k+1;

??????

? end if;

? vga_vs_control <= vs;?

END PROCESS ;

?

PROCESS (clk)

BEGIN

?????? if clk'event and clk = '1' and vs = '1' and hs ='1' then

????????????? vga_green_dispaly <= GRB(2);

??????

??? vga_read_dispaly? <= GRB(1);

????????????? vga_blue_dispaly? <= GRB(0);????????????????

????????? end if;

END PROCESS ;

?????? END a;